US008107622B2

# (12) United States Patent

Gressel et al.

(54) SYSTEM AND METHOD TO PRECLUDE MESSAGE MODIFICATION IN DATA AUTHENTICATION SYSTEMS THROUGH EFFICENT USE OF FEEDBACK IN CRYPTOGRAPHIC FUNCTIONS

(75) Inventors: Carmi David Gressel, Mobile Post

Negev (IL); Gregory Van Bard, Hartsdale, NY (US); Orr David Dunkelman, Ramat Gan (IL); Avi Hecht, Nesher (IL); Ran Granot, Yavne

(IL)

(73) Assignee: Fortress GB Ltd., London Greater

London (GB)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 261 days.

(21) Appl. No.: 12/439,556

(22) PCT Filed: **Sep. 6, 2007**

(86) PCT No.: **PCT/IL2007/001101**

§ 371 (c)(1),

(2), (4) Date: Jun. 3, 2009

(87) PCT Pub. No.: WO2008/029406

PCT Pub. Date: Mar. 13, 2008

(65) Prior Publication Data

US 2009/0304179 A1 Dec. 10, 2009

# Related U.S. Application Data

- (60) Provisional application No. 60/842,612, filed on Sep. 7, 2006, provisional application No. 60/928,616, filed on May 11, 2007.

- (51) Int. Cl.

H04L 9/28

(2006.01)

H04L 9/32

(2006.01)

G06F 17/10

(2006.01)

# (10) Patent No.: US 8,107,622 B2 (45) Date of Patent: Jan. 31, 2012

(52) **U.S. Cl.** ...... **380/28**; 713/181; 707/698

(56) References Cited

# U.S. PATENT DOCUMENTS

| 6,556,158 B2 * 2002/0114452 A1 * | 4/2003<br>8/2002 | Bernede et al.       380/44         Steensgaard-Madsen       341/131         Hamilton       380/42         Snell       380/28 |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| oited by exeminer                |                  |                                                                                                                               |

\* cited by examiner

## OTHER PUBLICATIONS

International Preliminary Report on Patentability for PCT/IL2007/001101; mailed Apr. 7, 2009—7 pages.

Primary Examiner — Aravind Moorthy (74) Attorney, Agent, or Firm — Roach Brown McCarthy & Gruber P.C.; Kevin D. McCarthy

#### (57) ABSTRACT

A data hashing system operative to hash an incoming string of message words is an object of the present invention. The system generates a hash value tag comprising a deterministic random number string which uniquely identifies the incoming string. The system comprises at least first and second register arrays, at least one 1-way functionality in at least pseudo-randomizing function; and a set of at least first and second orthogonal feedback word stream generators operative to generate a set of at least first and second orthogonal feedback streams of message words respectively, including applying respective permutations to the incoming string. Wherein the first and second feedback streams are combined into the first and second register arrays respectively, the at least pseudo-randomizing functionality accepts input from the register arrays and generates at least pseudo-random output which, in combination with a present word in the incoming string, is provided to the stream generators, and the first feedback stream is a first function of a present word in the incoming stream and the second feedback stream is a second function of a present and previous words, in the incoming stream.

## 24 Claims, 20 Drawing Sheets

FIG. 1A

FIG. 8

FIG. 6

**FIG. 11A**

FIG. 11C

# SYSTEM AND METHOD TO PRECLUDE MESSAGE MODIFICATION IN DATA AUTHENTICATION SYSTEMS THROUGH EFFICENT USE OF FEEDBACK IN CRYPTOGRAPHIC FUNCTIONS

#### REFERENCE TO CO-PENDING APPLICATIONS

Priority is claimed from a 371 of international of PCT/ IL2007/001101, filed on Sep. 6, 2007; which claims priority from U.S. Provisional Application No. 60/842,612, "A Feedback Strategy for the ZK-Crypt with Obviates Fraudulent Unkeyed Hash Collisions and Enhances Crypto-Complexity in Stream Cipher and True Random Number Generation", filed Sep. 7, 2006 and from U.S. Provisional Application No. 60/928,616, "Method and Apparatus for Increasing Unpredictability and for Secure Parallelization of Semiconductor Ciphers, Hashes and RNGs wherein Two Versions of Multibit Feedback are Reintegrated into Disparate Parts of a Digital Device", filed May 11, 2007

#### FIELD OF THE INVENTION

The present invention relates generally to systems and methods for data hashing, ciphering and random number  $^{25}$  generation.

# BACKGROUND OF THE INVENTION

Numerous methods and systems for hashing are known, <sup>30</sup> such as those described in Knuth, Donald (1973). *The Art of Computer Programming* vol. 3, Sorting and Searching, pp. 506-542.

Digital devices useful in conjunction with hashing systems are described in co-pending published PCT patent applications, WO 2005/101975 and WO 2007/0949628, also termed herein "975" and "628".

Applicant's World Wide Website located at fortressgb.com includes:

- a. A set of concept and circuit drawings describing the 40 ZK-Crypt functions

- b. An article entitled "Understanding the ZK-Crypts—Ciphers for (Almost) all Reasons".

- c. An article entitled, "A Security Analysis of the ZK-Crypt".

- d. A software simulator of the physical Noise Generator used to establish safe circuit parameters for the Random Controller in certain preferred embodiments of this patent.

The disclosures of all publications and patent documents 50 mentioned in the specification, and of the publications and patent documents cited therein directly or indirectly, are hereby incorporated by reference.

# SUMMARY OF THE INVENTION

Certain embodiments of the present invention seek to provide methods for Obviating Message Modification in Data Authentication while Increasing Complexity and Parallelization Thereof.

Certain embodiments of the present invention seek to provide methods for generating separate dense feedback streams and/or a combination of dense and sparse feedback streams in a multiplicity of at least one deterministic random number generator core configured particularly as a data authenticator 65 and/or as a stream cipher thereby to increase complexity and to obviate the generation of two data input strings which

2

generate a resulting identical state condition of a multiplicity of deterministic random number internal binary state variables

Certain embodiments of the present invention seek to provide configurations of multiple feedback streams circulating data in deterministic random number generator cores operative to be used in data authentication or cipher apparatus; thereby to increase diffusion of malicious or unintended changes in the source of the feedback and in particular the input binary data authentication strings, to obviate malicious or unintended Message modification.

Certain embodiments of the present invention seek to provide enhancement for single and for multi-purpose digital security modules with parallel feedback; operable to increase complexity and to provably and intuitively obviate malicious or unintended data modification in unkeyed and keyed hashing methods and apparatus.

A Hash function is typically an efficient one-way compres-20 sion of longer binary strings into fixed length strings, typically called Hash-Values (for hashes, keyed hashes or MACs), or Tags (typically for keyed hashes or MACs). In this document, Hash-Value and Tag are used interchangeably, and often in combination, Hash-Value Tag. In such data authentication systems, a user must be reasonably assured that any change in the binary input string, large or small, renders a false hash value. Typically, hash functions do not involve secrets, are publicly known, and a potential attacker knows the process of compression. The hash value, to be checked against the single value previously known hash value of the original binary string, is designed to reasonably assure a user of the authenticity of the data. A hash function, in which a secret key is used to initiate the apparatus, enables a user who knows both the secret key and the true hash-value to determine the integrity and, typically, with a level of assurance, the origin of the "hashed" data. An apparatus with a secret key is typically classified as a MAC, a Message Authentication Code; or an HMAC, a Hashed MAC. For historic reasons, in this patent an Engine is in MAC Mode, when the feedback streams are a function of the Cipher Mask XORed to the Message Word, where in some instances the Message Word is equal to zero.

Both Hash and MAC functions use deterministic random number generator, DRNG, cores to produce pseudo-random internal values. These internal values are then combined with binary data input strings wherein the combination is fed back and diffused into the state variables of the DRNG. In this patent the DRNG typically refers to the total circuitry which executes Hash and Stream Cipher functions as an Engine. The Engine is viewed in three major parts, the Random Controller, which regulates permutations in the larger part of the Engine, the 32 Bit Word Manipulator, which is referred to generically as the Word Manipulator (which includes the Register Bank 55 and Data Churn) and the Result & Feedback Processor. This document is designed first and foremost based on the operations of the Word Manipulator and the Result and Feedback Processor, which is fed by and feeds back orthogonal diffusing vectors to the Word Manipulator. For the purposes of explaining the principals of orthogonal feedback streams it is assumed that the Random Controller is irrelevant during the well planned adversarial attack; as the astute Adversary has probably chosen a favorable window for attack. The two sets of tiers in the Register Bank are each two subset DRNGs and the Data Churn is also referred to as a subset DRNG. This is compliant with engineering nomenclature, wherein the nLF-SRs in the Register Bank are referred to as pseudo-random

number generators; and the diffusive correlation immunizing hybrid filters and displacement matrices in the Data Churn constitute efficient DRNGs.

Two or more data authentication feedback streams are defined as orthogonal if a sequence of Message Words causes one stream to successfully corrupt and reconcile one section of tiers in the Register Bank; wherein the second feedback stream simultaneously irreconcilably corrupts at least one other section of the Register Bank for every possible corrupting Message Word. This is intuitively obvious, but difficult to 10 prove logically, in all cases. Included are a flow chart and two source C codes, which check and prove orthogonality for all possible 2<sup>32</sup> false message words, for shift registers and for rotating registers. The proof for static memory store registers is included separately, where the two Orthogonal feedback 15 functions are simply the two stored feedback 32 bit words:

A=Present (Cipher Mask XOR Message Word); SUP, and B=A XOR Previous (Cipher Mask XOR Message Word),

Dense feedback, especially wherein all feedback words are 20 simple rotated versions of the same Results, generates strongly correlated output Cipher Mask words, and resulting poor statistics. Hence in certain preferred embodiments the feedback sources of each stream are typically uncorrelated and permuted. In certain preferred embodiments, the Result is 25 the XOR sum of the Cipher Mask, the output of the 32 bit Data Manipulator, a DRNG, and the Message Word. The output of the Result store is the Previous Result. The input to the Result store is the Present Result.

The inventive step in this patent assures orthogonality 30 when two or more disparate feedbacks streams are XOR summed to two or more sets of static, rotating or shifting registers; e.g., static memory stores, nLFSRs, LFSRs, simple shift registers and/or rotating registers.

One stream is sourced from at least the XOR sum of a 35 Previous and a Present Result Word; i.e., the Lower Feedback in certain preferred embodiments, and the second source is a function of at least the Present Result word, and is only affected by false bits in a Present Result word; i.e., the Super Tier Feedback in certain preferred embodiments. The first 40 false Message Word uniquely affects the Present Result only, hence both feedbacks affect the same number of indexed bits in each Register set. Register bits are indexed from left to right, 0 to 31, wherein 31 is the MS (most significant) register

In order that an attack may succeed, on the next clock cycle, both feedback streams typically simultaneously reconcile all falsified bits in their respective registers.

In the next clock cycle a second false Message Word must be contrived to reconcile falsified bits in at least one of the 50 register sets. In order to generate a reconciling word for the Lower Feedback, the known unique feedback word is the XOR sum of the falsified Previous Result (with the same false bits as the previously falsified Message Word) and falsified Present Result output words (with the same false bits as the 55 embodiment are shown which invite malicious attempts to presently falsified Message Word).

The Super Tier Feedback is the new falsified Message Word bits reflected in the Present Result only. In certain preferred embodiments, this second feedback may or may not reconcile previously generated false bits in the Super Tier, but 60 provably leaves a trace of false bits.

If the receiving register sets are static, same index false bits (now reconciling bits) are typically XOR summed on the second clock to the Lower Feedback register set. In such a case, the Message Word is true (no falsified bits), as the 65 previous Message Word false bits residing on the output of the Result store, reconcile the Lower Feedback register set.

In such a case, the Message Word is true (the Present Result is true); therefore all false bits in the Super Tier from the previous clock typically remain.

As certain preferred semiconductor embodiments of the Engines typically occupy a small fraction of a chip area, implementing two or more Engines on new semiconductor devices with CPUs, to enable fast, compact, state of the art, low current consumption for:

True Random Number Generation;

En/Decryption (Stream Cipher); and,

Data Authentication (Hash or MAC)

Efficient methods of concatenating preferred embodiment Engines to increase throughput and complexity for highest security are shown, paving the way to highest security applications, and simultaneous Decryption and Data Authentica-

The robust feedback schemes, where at least two orthogonal feedback streams are generated by at least one DRNG are described. Stated differently, in certain preferred embodiments two or more feedback streams are orthogonal feedbacks wherein for any change in any state variables in either the Word Manipulator or the Result & Feedback Processor, the two or more feedback streams each changes different sections of state variables in the Engine such that later feedback changes typically cannot reconcile the Engine to a previous valid state. There is typically no way that an adversary can change one or more Message Words; followed by valid Message Words, without leaving a random irreconcilable trace in the state variables of the Engine. E.g., in a hash digest an adversary cannot move or remove a decimal point, and then change another one or small number of Message Words without corrupting the Engine's state variables; thereby typically deterministically causing a subsequent false Hash Value Tag.

For a single bit change in a Message Word, the mutual source of both orthogonal feedback streams in the single Engine preferred embodiments, deterministically affects (diffuses into) the equations of an average of more than 160 Engine binary state variables in a first false Message Word cycle. In a linked concatenated plurality of at least two Engines, a single change in one Engine typically propagates spontaneously in an uncontrollable chain reaction.

Typical linear parallel feedback in DRNGs degenerates 45 output statistics measured with DieHard. Adding a second orthogonal feedback stream obviated message modification and improved both TRNG (True Random Number Generation) and Stream Cipher statistics.

Typically, an adversary, in his efforts to gain value, attempts a simple ploy of changing only a few bits of a message; where he knows how the Hash or MAC DRNG is designed, and has a good idea of how to reconcile binary state variables to a valid state. Weaknesses in two single track feedback reduced architecture versions of a preferred generate a "second preimage" attack; i.e., a modified data input string that subsequently reconciles state variables of the DRNG to a typically identical or close to identical state.

A definition of a pre-image resistant hash function  $f(\cdot)$ , given x, it is hard to find x' such that f(x)=f(x'). In these practical cases, the Adversary wants x to closely resemble x'; e.g., a long text resembles the original, except for a few numbers which could be falsified. For an astute hacker to generate this type of meaningful pre-image, she must first generate at least one fraudulent Message Word to corrupt at least a portion of the Register Bank, and then generate a Message Word sequence which must successfully reconcile

typically all of the hundreds of internal variables of the Engine to an original condition.

Such a ruse cannot work in a single feedback stream embodiment; wherein one Message Word's fault bits appear in two consecutive clock cycles. However, the scam demonstrates a weakness that is conclusively remedied by a second orthogonal feedback.

It is shown that concatenating Engines with linked feedback streams enormously increase complexity and potentially multiply single Engine speeds at a low cost.

If there are only two concatenating devices the feedback interlinking system is called a feedback swap, wherein the Left Engine switches in its Right Hand neighbor's Right Lower Feedback to replace its Left Lower Feedback which is fed into the Right Hand Engine. If more than two Engines are 15 involved all, except the "last" MS (most significant) Engine, feeds its Lower Feedback to replace its near neighbor's Lower Tier Feedback; wherein the MS Lower Feedback is fed into the LS (Least Significant) Engine.

Any attempt to modify one Message Word in one Engine 20 results in corrupting its own Super Tier and its neighbor's TMB (Top, Middle and Bottom) Tiers and Data Churn. Any attempt to reconcile, typically entails further corrupting of at least one of the two Engine's Register Bank.

In another preferred embodiment, if two or more Engines 25 are interlinked, all engines, except the "last" MS Engine, feed their Super Tier Feedback XOR summed to their near neighbor's Super Tier Feedback; where only the LS Engine XOR sums its Cipher Mask Count (HAIFA) with its own Super Tier feedback

The maximum speed attainable, and the current consumption of concatenated units is typically a linear function of the number of Engines. The cryptocomplexity is typically an exponential function of significant binary variables in the Engines.

A Cipher Mask Counter is used to generate interrupts and to synchronize and paginate transmissions. In data authentication regimes, the counter output is XOR summed to the value in the Super Tier Register to assure that at each clock cycle a valid state includes the index number of the Cipher 40 Mask. This scheme was suggested by "HAIFA" to prevent preassembling false Messages in sections to be moved at will in a shift regist small number new positions. A Hash/MAC a) one or more in a final false Message stream.

Having two or more configurable identical Engines, with and without optional Lower Feedback concatenation, has 45 additional advantages. Organized as two Engines which optionally can accept the same input data, one half of the Engines can hash while the other half decrypts. Except for initialization, and final generation of the Hash-Value Tag, both Engines receive the same input data, wherein only the 50 clear text value is output from the decrypting Engine. During the following verification sequence only the MAC Mode Engine or linked Engines are read. At the end of the verification step, the user typically knows if the clear text is valid. Typically, only then, error correction is necessary on clear 55 text. As Stream Ciphers do not propagate errors, as opposed to Block Ciphers in feedback mode, error correcting clear text only when necessary is less costly than error correcting/detecting all cipher text, as conventionally done in block cipher encryption.

The suggest Hash-Value Tag calls for 16 unread scrambles which may be pre-appended to the presently defined Hash-Value Tag., potentially adding 512 bits to the tag length.

Classic Attacks on a Hash or a MAC are now described. The classic attack on a MAC apparatus is simple. Complement (flip) bits in a Message in one clocked cycle and then in a subsequent clock cycle flip the same index bit—it can

6

happen that the second flipped bit reconciles the falsified bit; without leaving a trace in any of the Engine variables. This is typically the first attack used by an attacker with no knowledge of the Engine architecture. An adversary who has knowledge of certain preferred embodiments uses the same concept, and assures that most significant cells of nLFSRs is not complemented, and realizes that the first cut corrupted bits move right one cell at the next clock.

To show the efficacy of the dual feedback system, fault vectors are generated typically wherein defined bits in a Word are false. The XOR symbol is used to demonstrate corruption and reconciliation of binary variables. A False bit means a bit of opposite polarity (complemented) from a True bit; therefore if a true binary value, T, is equated to "0", and F a false value to "1" then conventional XOR logic holds as:

$T \oplus T = T$ ;  $T \oplus F = F$ ;  $F \oplus T = F$ ; and  $F \oplus F = T$ .

If a Message bit is false and is encoded (XORed to assure a change in the feedback) with a true bit of a Cipher Mask, the result is the opposite polarity of the truth, hence false. If a new false feedback bit is XORed to the corrupted (false) bit(s), the resulting bit or bits (assuming that three or four same index bits in the Register Bank were corrupted) is/are all be reconciled, with no apparent trace left in the Register Bank.

As stated above, attacking certain preferred embodiments of this patent is more complicated, as the attacker is "shooting at moving targets". The active components of the Tiers of the Register Bank are nLFSRs which when clocked move bits from a left hand cell into a right hand cell. Because of the structure of the nLFSRs, all cells except the MS (most significant cell) of an nLFSR can be flipped (falsified) on one clock cycle, and then reconciled on the next clock cycle. That means that potentially 28 of the 32 Message Word bits are auspicious (for the attacker) which can be falsified and then reconciled by two consecutive false Message Words. The clocked tiers in the Register Bank that are falsified, right shift bits one cell at every clock. If the attacker complements bit(s) in a shift register, she must reconcile the bit(s) a cycle (or a small number of cycles) later as falsified bit are shifted into

A Hash/MAC Attack of this Type is Successful if:

- a) one or more falsified bits complemented in one or more Message Word can be inserted in a Message sequence followed by a second reconciliation Word or Word sequence contrived such that the following sequence of Messages reconciliates sufficient binary state variables in the Engine, to assure that a true Hash-Value Tag can be generated; or,

- b) the adversary can choose a likely candidate Message Word to falsify and subsequently generate an auspicious word containing only error bits that do not cause subsequent propagation of false signals into the Random Controller, or leave traces (irreconcilable falsified bits) in the Register Bank, the Data Chum or the Result/Feedback Processor; and,

- c) after generation of the first falsifying/reconciling Message Word pair (or short sequence), subsequent Message Words can be generated which cause valid feedback (the same feedback sequence generated in the original Message string digest) to maintain components that normally retain "historical evidence of false words" (the Register Bank and Store & XORs) in a valid condition, so that at the end of the Message Word string digest the binary variables are in the true unextended condition and can generate a true Hash-Value Tag.

The attacker has the best chance of success, if she reconciles the falsified bit(s) on the immediately following clock

cycle. As can be seen in certain preferred embodiments in the Description of the Figures—assume that an attacker has falsified the LS bits in the Register Bank, and she waited 16 cycles to insert a reconciling word. On the 12th cycle the falsified bit has corrupted the Top Left nLFSR as the moving 5 false bit corrupted the MS nLFSR feedback bit; on the 14th cycle it has corrupted the Bottom Left nLFSR; and on the 15th cycle it has corrupted the Left Super Tier nLFSR. It is also mandatory that the corrupted tiers shift together for the reconciliation bit to be able to re-complement all falsified bits. In 10 certain preferred embodiments, the same tiers rarely rotate together for more than five consecutive Primary Clock cycles.

Many Message Words are valid candidates to enable the two step falsifying and rectification of the Register Bank without affecting the Random Controller. In the two step 15 sequence, in a preferred embodiment, up to 28 bits of candidate words can be falsified without complementing the MS (internal feedback bits) of the Register Bank nLFSRs. In a generalizing case of a 32 bit architecture, wherein all nLFSRs are 32 bit long, up to 31 bits can be corrupted.

In these analyses, it is assumed that the adversary has chosen a most auspicious word that corrupts the Register Bank, the Data Churn and the Result Store, on the first cycle, and reconciles the Register Bank on the next cycle. As described herein, typically, even if she "contrived" the best of 25 all possible words, the attack does not work.

The feedback tracks linearly aberrate (change from the "expected") binary state variables in the Register Bank and the Data Churn. In MAC Mode, a complemented bit in a valid Message Word complements indexed bit in the clocked tiers 30 of the Register Bank two clock cycles later. Flipped Message Word bits are inserted into the Feedback Stores on the next clock. Two clocks later the flipped bits affect the Register Bank and the Data Churn. Only tiers that are clocked are affected by feedback. For simplicity it is assumed that all four 35 Tiers are clocked together. If the i'th bit is complemented, at the next clock the i'th bit is shifted into the i+1'th cell(s). As the complemented bit is shifted into the i+1'th cell, it can simultaneously be re-complemented by a false complemented feedback bit in the next clock cycle. In this most 40 efficient method, the second false reconciling Message Word reconciles the Register Bank (in Single Feedback mode), immediately. In certain preferred embodiments, attempts at reconciling false bits with a wait of more than two cycles is even less tractable, as internally generated feedback (not rec- 45 oncilable by attacker generated Message Words) typically uncontrollably corrupts the Super Tier and the Data Churn.

An attack on the unenhanced embodiment commences with an altered Message Word submitted at stage  $t=t_{i-1}$  (acting on the register bank at the i+1'th stage); and at stage  $t=t_i$  50 a retrieval word is submitted to revert the Register Bank to a valid state at the i+2'th stage; contrived message words are input so that at stage  $t=t_{i+7}$  all variables in the Data Manipulator have reverted to the original sequenced values for both previous valid and previous fraudulent Message Words; assuming that the minimal preconditions have been fulfilled. Therefore, after the i+7'th contrived Message Word is enacted, all original Message Words are valid; and the final resulting Hash-Value Tag on the valid and fraudulent "Authenticated Message Strings" are identical.

If at the end of the Message Digest, all variable polarities are in the valid state, the Hash-Value Tag is valid, regardless of any previous events.

Note again, the total status of all state variables cannot be rectified if any of the index bits 12, 14, 15, 17 and/or 31 of the 65 first fraudulent Message Word has been complimented. In such cases, at least one nLFSR MS cell causes a faulty un-

8

retrievable One to Many nLFSR permutation. Note also, as the Register Bank tiers "accept" the fraudulent word, they execute a one cell rotate at each clock, such that the "retrieving" false vector whose function is to rectify all complemented values in the Register Bank, is generated on the next clock cycle. Therefore, only 27 or 28 of the 32 Message Bits can successfully be complemented on the first fraudulent Message Word. These 27 or 28 bits are potentially "auspicious bits". In the enhanced feedback version of this invention, a fraudulent word immediately causes irretrievable variable complementations in the Register Bank, the Data Churn and the Result/Feedback Processor; and typically in a few clock cycles corrupts the Random Controller.

An auspicious stage is one condition of the Engine variables where it is potentially possible to complement some or all of the above mentioned 28 bits of a valid Message word, and subsequently successfully reconcile the Register Bank to its original state with a second fraudulent Message Word on the next clocked stage. Once having successfully changed one bit of a Message Word, changing up to 28 bits of the Message Word is a trivial exercise for an adversary who knows the initial condition of the unenhanced embodiment.

During the window of auspicious changes, a necessary condition is that there are no uncontrollable changes in the Register Bank or Random Controller for two clocked cycles.

This means, at least, that the following conditions are observed for a successful attack which commences with the submission of the i-1'th Message Word:

- MS bits of the 8 Register Bank nLFSRs are never permuted by the first faulty word; e.g., the adversary can only permute up to 28 auspicious bits;

- 2) that for the two critical clocked cycles, i+1'th and i+2'th cycles, only the same tiers are activated, most typically, all four tiers; since otherwise the proper reversions are not effected on all of the i+1'th clock cycle affected tiers; and

- 3) the serial feedback string from the Top Splash Matrix to the Splash Selector, is not changed for the i+2'th or the i+3'th clocked cycles.

During the i+2'th to 1+6'th critical clocks, any changes in the Data Chum are temporal and irrelevant, iff the relevant Message Words are properly contrived, as a reconciled Register Bank quickly reconciles the Data Churn, if valid sustainable feedback is generated.

There is thus provided, in accordance with certain embodiments of the present invention, a data hashing system operative to hash an incoming string of message words, thereby to generate a hash value tag comprising a deterministic random number string which uniquely identifies the incoming string of message words, the system comprising at least first and second register arrays; at least one 1-way at least pseudorandomizing functionality; and a set of at least first and second orthogonal feedback word stream generators operative to generate a set of at least first and second orthogonal feedback streams of message words respectively, including applying respective permutations to the incoming string of message words, wherein the first and second feedback streams are combined into the first and second register arrays respectively; wherein the at least pseudo-randomizing functionality 60 accepts input from the register arrays and generates at least pseudo-random output which, in combination with a present word in the incoming string, is provided to the stream generators, and wherein the orthogonal feedback streams are characterized in that every possible modified incoming string of message words which differs by at least a single word from an original incoming string of message words has at least one of the following two characteristics (a) and (b):

g

a. the modified incoming string causes a corrupting first feedback stream generated by applying a permutation to the modified incoming string, when combined into the first register array, to corrupt the first register array, relative to the same first register array into which a non-corrupting first feedback stream, generated by applying the permutation to the original incoming string, has been combined; and/or

b. the modified incoming string includes at least one reconciling word which enables the modified incoming string, when permuted to form one first feedback stream which is 10 combined into the first register array, to reconcile the first register array relative to the same first register array into which a modified first feedback stream, formed by permuting the original incoming string of message words, has been combined, however the at least one reconciling word in the 15 modified incoming string of message words causes a corrupting second feedback stream generated by applying a permutation to the modified incoming string, when combined into the second register array, to corrupt the second register array, relative to the same second register array into which a non- 20 corrupting second feedback stream, generated by applying the permutation to the original incoming string, has been combined.

Further in accordance with certain embodiments of the present invention, the system also comprising first and second 25 functionalities associated with the first and second register arrays respectively, wherein at least one of the first and second functionalities comprises a one-way randomizing functionality.

Still further in accordance with certain embodiments of the 30 present invention, the first and second feedback streams are XOR summed into the first and second register arrays respectively.

Further in accordance with certain embodiments of the present invention, at least one of the first and second register 35 arrays comprises at least one non-linear feedback register.

Additionally in accordance with certain embodiments of the present invention, the first feedback stream is a first function of a present word in the incoming stream and wherein the second feedback stream is a second function of the present 40 word, and of a previous word, in the incoming stream.

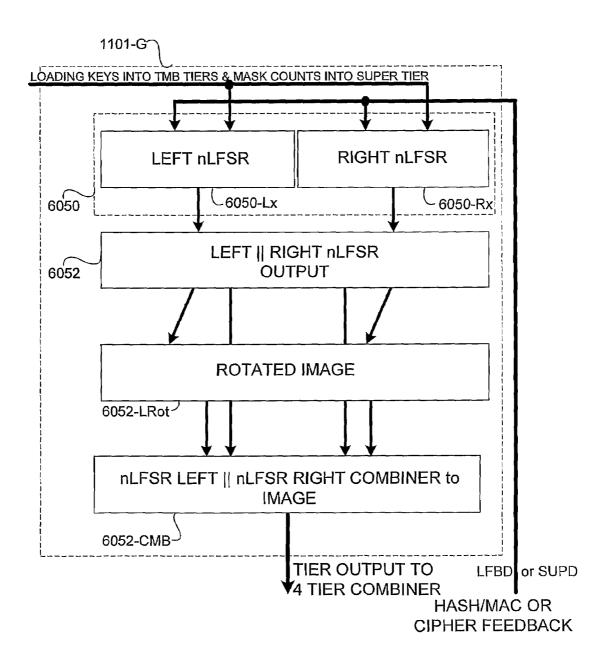

Further in accordance with certain embodiments of the present invention, at least one of the first and second register arrays comprises a set of at least one non-linear feedback shift registers.

Still further in accordance with certain embodiments of the present invention, an output of the non-linear feedback register is rotated, thereby to form an image of the output which is recombined with the output of the non-linear feedback register.

Further in accordance with certain embodiments of the present invention, the image of the output is randomly recombined with the output of the non-linear feedback register.

Still further in accordance with certain embodiments of the present invention, at least one of the first and second register 55 arrays comprises six different non-linear feedback registers arranged in three concatenated pairs.

Further in accordance with certain embodiments of the present invention, for each of the three pairs, an output of the pair of non-linear feedback registers is rotated, thereby to 60 form an image of the output which is recombined with the output of the pair of non-linear feedback registers, thereby to generate three tiers, each comprising a respective one of the three concatenated pairs of non-linear feedback registers.

Still further in accordance with certain embodiments of the 65 present invention, an output of the three tiers is combined in a 2-of-3 majority combiner.

10

Further in accordance with certain embodiments of the present invention, the system also comprises a message counter generating a binary output which is XOR-summed to at least one of the first and second feedback streams.

Still further in accordance with certain embodiments of the present invention, there is provided a pair of first and second data hashing systems as described above, wherein at least one of the first and second feedback streams is swapped between the first and second data hashing systems such that at least one feedback stream entering at least one of the register arrays in the first hashing system is generated by the second hashing system whereas at least one feedback stream entering at least one of the register arrays in the second hashing system is generated by the first hashing system.

Further in accordance with certain embodiments of the present invention, a sequence of data hashing systems as described above is provided, wherein at least one feedback stream entering at least one of the register arrays in each hashing system in the sequence is generated by the next hashing system in the sequence and wherein at least one feedback stream entering at least one of the register arrays in the last hashing system in the sequence is generated by the first hashing system in the sequence.

Still further in accordance with certain embodiments of the present invention, at least one 1-way at least pseudo-randomizing functionality comprises stream cipher functionality.

Further in accordance with certain embodiments of the present invention, the feedback word stream generators receive inputs from the stream cipher functionality and are independent of the incoming stream of message words.

Still further in accordance with certain embodiments of the present invention, the system also comprises clock apparatus which randomly regulates at least one of the register arrays, the randomizing functionality, and the feedback stream generators, thereby to provide true randomness.

Also provided, in accordance with certain embodiments of the present invention, is a data hashing method operative to hash an incoming string of message words, thereby to generate a hash value tag comprising a deterministic random number string which uniquely identifies the incoming string of message words, the method comprising providing at least one 1-way at least pseudo-randomizing functionality; and using a set of at least first and second orthogonal feedback word stream generators to generate a set of at least first and second 45 orthogonal feedback streams of message words respectively, including applying respective permutations to the incoming string of message words, wherein the first and second feedback streams are combined into first and second register arrays respectively, wherein the at least pseudo-randomizing functionality accepts input from the register arrays and generates at least pseudo-random output which, in combination with a present word in the incoming string, is provided to the stream generators, and wherein the orthogonal feedback streams are characterized in that every possible modified incoming string of message words which differs by at least a single word from an original incoming string of message words has at least one of the following two characteristics (a) and (b):

a. the modified incoming string causes a corrupting first feedback stream generated by applying a permutation to the modified incoming string, when combined into the first register array, to corrupt the first register array, relative to the same first register array into which a non-corrupting first feedback stream, generated by applying the permutation to the original incoming string, has been combined; and/or

b. the modified incoming string includes at least one reconciling word which enables the modified incoming string,

when permuted to form one first feedback stream which is combined into the first register array, to reconcile the first register array relative to the same first register array into which a modified first feedback stream, formed by permuting the original incoming string of message words, has been combined, however the at least one reconciling word in the modified incoming string of message words causes a corrupting second feedback stream generated by applying a permutation to the modified incoming string, when combined into the second register array, to corrupt the second register array, relative to the same second register array into which a noncorrupting second feedback stream, generated by applying the permutation to the original incoming string, has been combined.

Further provided, in accordance with certain embodiments of the present invention, is a data hashing method operative to hash an incoming string of message words, thereby to generate a hash value tag comprising a deterministic random number string which uniquely identifies the incoming string of 20 message words, the method comprising providing at least one 1-way at least pseudo-randomizing functionality; and using a set of at least first and second orthogonal feedback word stream generators to generate a set of at least first and second orthogonal feedback streams of message words respectively, 25 including applying respective permutations to the incoming string of message words, wherein the first and second feedback streams are combined into first and second register arrays respectively, wherein the at least pseudo-randomizing functionality accepts input from the register arrays and generates at least pseudo-random output which, in combination with a present word in the incoming string, is provided to the stream generators, and wherein the first feedback stream is a first function of a present word in the incoming stream and wherein the second feedback stream is a second function of the present word, and of a previous word, in the incoming

Additionally provided, in accordance with certain embodiments of the present invention, is a data hashing system 40 a register storing a plurality of state variables, copy A having operative to hash an incoming string of message words. thereby to generate a Hash-Value Tag comprising a deterministic random number string which uniquely identifies the incoming string of message words, the system comprising at least first and second register arrays; at least one 1-way at least 45 pseudo-randomizing functionality; and a set of at least first and second orthogonal feedback word stream generators operative to generate a set of at least first and second orthogonal feedback streams of message words respectively, including applying respective permutations to the incoming string 50 of message words, wherein the first and second feedback streams are combined into the first and second register arrays respectively, wherein the at least pseudo-randomizing functionality accepts input from the register arrays and generates at least pseudo-random output which, in combination with a 55 present word in the incoming string, is provided to the stream generators, and wherein the first feedback stream is a first function of a present word in the incoming stream and wherein the second feedback stream is a second function of the present word, and of a previous word, in the incoming 60

The following terms, where used, are intended to include, at least as an alternative, the following meanings respectively:

Orthogonal: A set of more than two feedback streams are orthogonal if each pair of feedback streams within the set is 65 orthogonal. A pair of feedback streams is orthogonal if every possible modified incoming string of binary words which

12

differs by at least a single word from an original incoming string of binary words has at least one of the following two characteristics (a) and (b):

a. the modified incoming string causes a corrupted first feedback stream generated by applying a permutation to the modified incoming string, when combined into the first randomizing functionality, to corrupt the first randomizing functionality, relative to the same first randomizing functionality into which a non-corrupted first feedback stream, generated by applying the permutation to the original incoming string, has been combined;

b. the modified incoming string includes at least one reconciling word which enables the modified incoming string, when permuted to form one first feedback stream which is 15 combined into the first randomizing functionality, to at least partially reconcile the first randomizing functionality relative to the same first randomizing functionality into which a modified first feedback stream, formed by permuting the original incoming string of binary words, has been combined, however the at least one reconciling word in the modified incoming string of binary words causes a corrupting second feedback stream generated by applying a permutation to the modified incoming string, when combined into the second randomizing functionality, to corrupt the second randomizing functionality, relative to the same second randomizing functionality into which a non-corrupting second feedback stream, generated by applying the permutation to the original incoming string, has been combined.

XOR, XOR summation: Addition modulo two of 2 single bits or the bitwise modulo 2 addition of the same index bits of two words, the process typically denoted by the "\theta" symbol; e.g.,  $1 \oplus = 0$ ;  $1 \oplus 0 = 1$ ; 1010 | 1100 = 0110.

Scramble: A deterministic permutation designed to increase adversarial intervention.

Corrupt: Given two copies A and B of a functionality storing and employing a plurality of state variables, copy A is said to have been corrupted if at least one of the state variables has been flipped relative to copy B.

Reconcile: Given a corrupted copy A and a true copy B of been corrupted by flipping a subset of the plurality of state variables relative to the values assigned to the same state variables in copy B, copy A is said to have been reconciled if all variables in the subset have been restored to their true values i.e. to the values assigned to these variables in copy B.

Data authentication: Confirmation that at least one characteristic, such as content and/or identity of originator, of a given body of data, also termed herein a "Message" and typically comprising a binary string, has not been modified.

Digestion: Applying a one-way function to incoming data in a way that each Message bit is reflected in a change of the Engine variables.

Time and Clock Cycles: Time, generally refers to the typically constant relation of states in variables, whereas Clock Cycles typically relate explicitly to a sequence of typically asymmetric events regulated by the Host. Hence, t+1 generally relates to a state one clock cycle later.

Any suitable processor, display and input means may be used to process, display, store and accept information, including computer programs, in accordance with some or all of the teachings of the present invention, such as but not limited to a conventional personal computer processor, workstation or other programmable device or computer or electronic computing device, either general-purpose or specifically constructed, for processing; a display screen and/or printer and/or speaker for displaying; machine-readable memory such as optical disks, CDROMs, magnetic-optical discs or other

discs; RAMs, ROMs, EPROMs, EEPROMs, magnetic or optical or other cards, for storing, and keyboard or mouse for accepting. The term "process" as used above is intended to include any type of computation or manipulation or transformation of data represented as physical, e.g. electronic, phenomena which may occur or reside e.g. within registers and/or memories of a computer.

The above devices may communicate via any conventional wired or wireless digital communication means, e.g. via a wired or cellular telephone network or a computer network 10 such as the Internet.

The apparatus of the present invention may include, according to certain embodiments of the invention, machine readable memory containing or otherwise storing a program of instructions which, when executed by the machine, implements some or all of the apparatus, methods, features and functionalities of the invention shown and described herein. Alternatively or in addition, the apparatus of the present invention may include, according to certain embodiments of the invention, a program as above which may be written in any conventional programming language, and optionally a machine for executing the program such as but not limited to a general purpose computer which may optionally be configured or activated in accordance with the teachings of the present invention.

Any trademark occurring in the text or drawings is the property of its owner and occurs herein merely to explain or illustrate one example of how an embodiment of the invention may be implemented.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Certain embodiments of the present invention are illustrated in the following drawings:

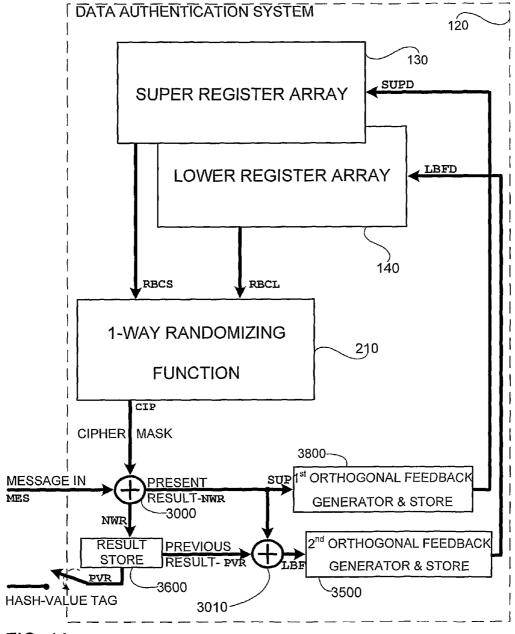

FIG. 1A is a simplified functional block diagram illustra- 35 ments of the Super Tier feedbacks. tion of a data hashing system constructed and operative in accordance with an embodiment of the present invention. FIG. 14A is a simplified block of example which typifies a mess

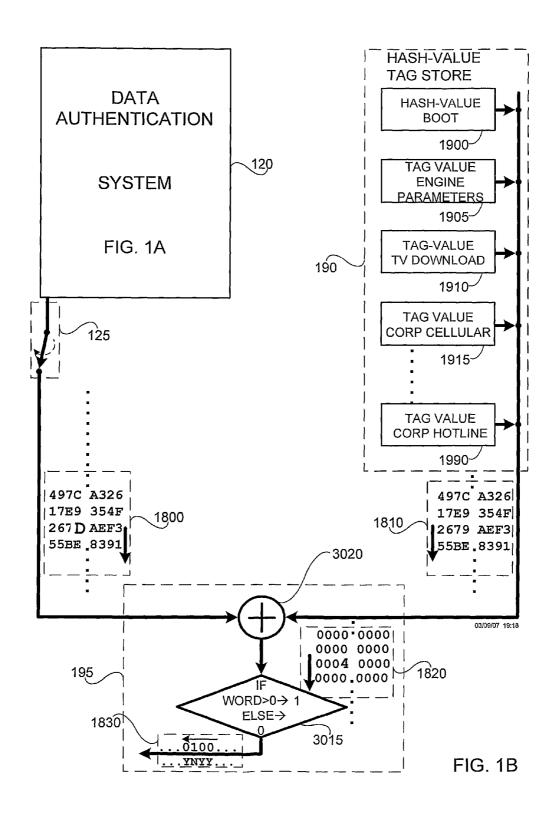

FIG. 1B is a simplified functional block diagram illustration of a data authentication system using the data hashing system of FIG. 1A, all in accordance with certain embodi- 40 ments of the invention.

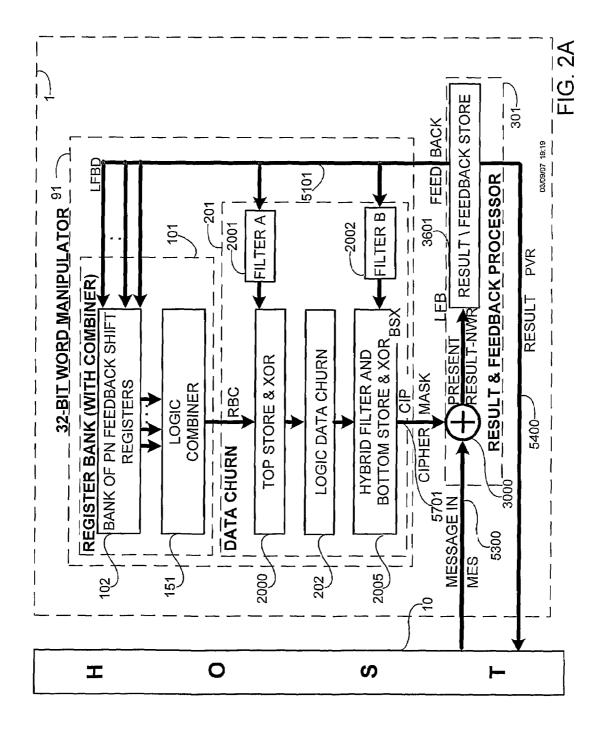

FIG. 2A is a simplified block diagram illustration of a class of hardware Word Manipulator apparatus which is typically susceptible to classical Message Word modification attacks.

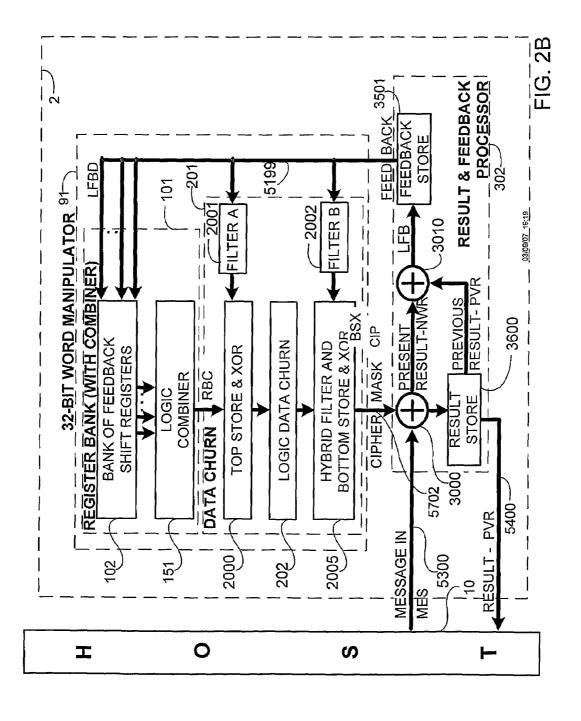

FIG. **2**B is a simplified block diagram illustration of a 45 configuration similar to FIG. **1** wherein the word Feedback is the XOR sum of the Previous and Present Results; it is appreciated that simple Message modification with complete short term reconciliation to valid states is impossible, even if an omniscient attacker can freely manipulate Message Words. 50

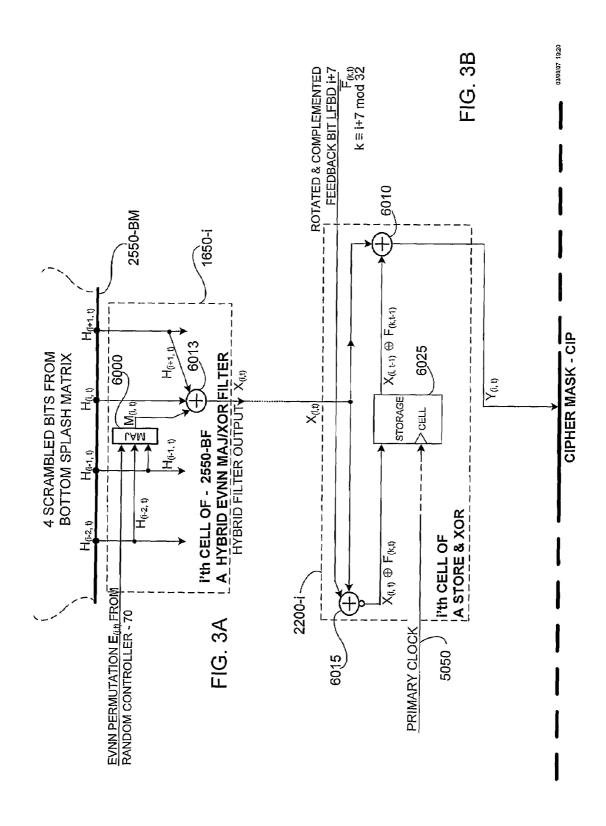

FIG. 3 is a simplified block diagram illustration of a single cell of the applicant's proprietary word length hybrid MAJ/3XOR non-linear/linear filter coupled to applicant's proprietary Store & XOR cell operative to receive a single feedback bit.

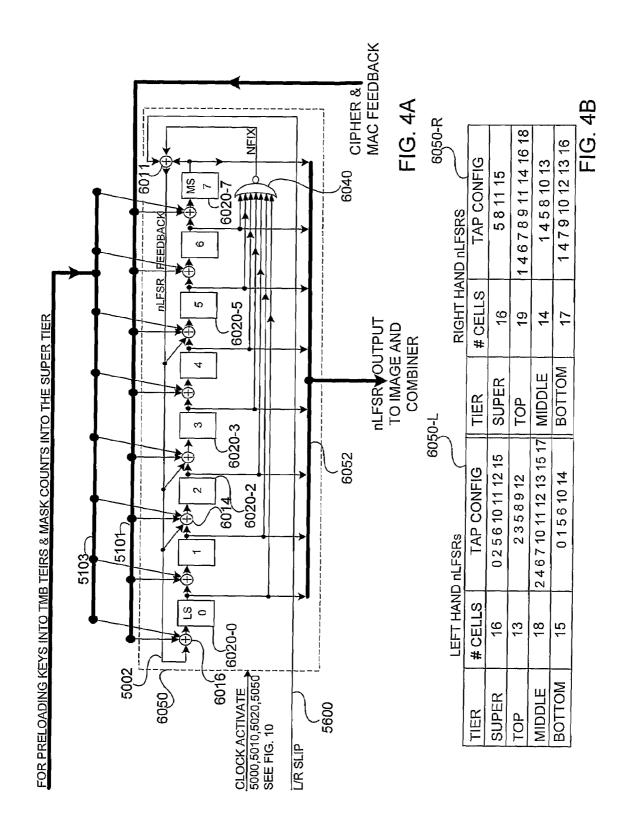

FIG. 4A is a simplified block diagram illustration of typical input and output variables; and the pseudo-random essentials of the 8 non-linear Feedback Shift Registers (nLFSRs) in certain preferred embodiments. The table of FIG. 4B documents the maximum length tap configurations of the left and 60 right hand nLFSRs of the 4 tiers of the Register Bank.

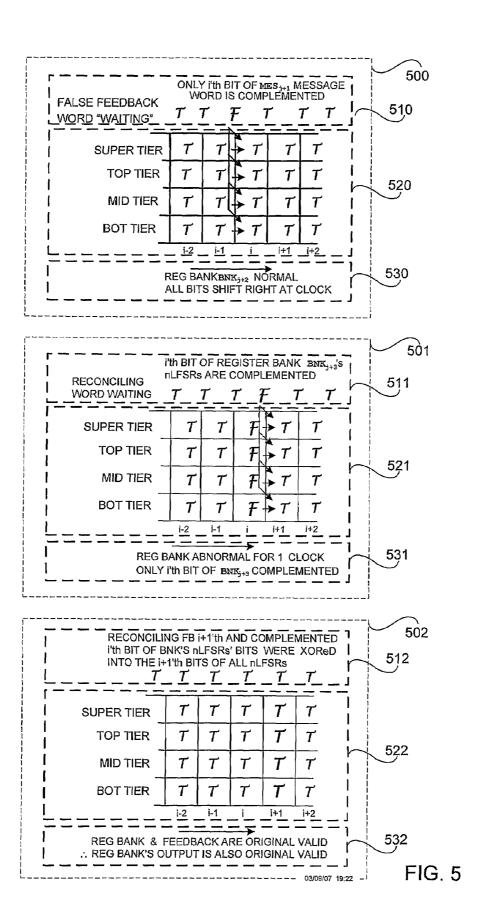

FIG. 5 is a simplified block diagram illustration showing how a faulty bit in a first Message Word via a single feedback configured Register Bank can, in auspicious circumstances, reconcile the Register Bank with a second faulty bit.

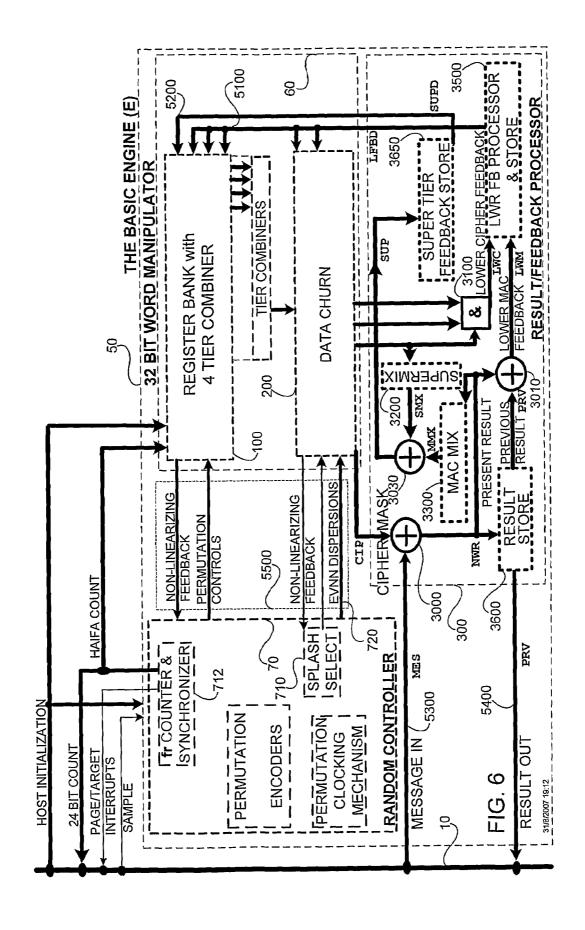

FIG. 6 is a simplified block diagram illustration of the Engine in certain preferred embodiments of this patent, show-

14

ing the three main components of the Basic Engine; i.e., the 32 Bit Word Manipulator, which includes the Register Bank and the Data Churn, the Result/Feedback Processor, and the Random Controller.

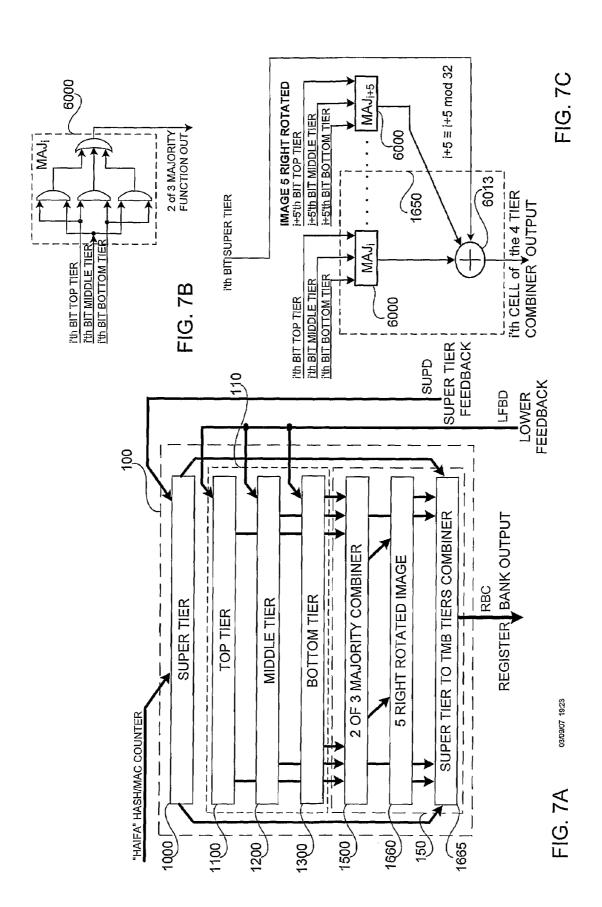

FIG. 7A is a simplified block diagram illustration of a basic architecture of the Register Bank of certain preferred embodiments. The output of the TMB (Top, Middle and Bottom) Tier outputs are combined in the 32 cells of the non-linear 2 of 3 Majority gates (MAJ in the drawings) depicted in FIG. 7B. FIG. 7C depicts a cell of the hybrid 4 tier combiner.

FIG. **8** is a simplified block diagram illustration of a structure of each of the four tiers of the Register Bank.

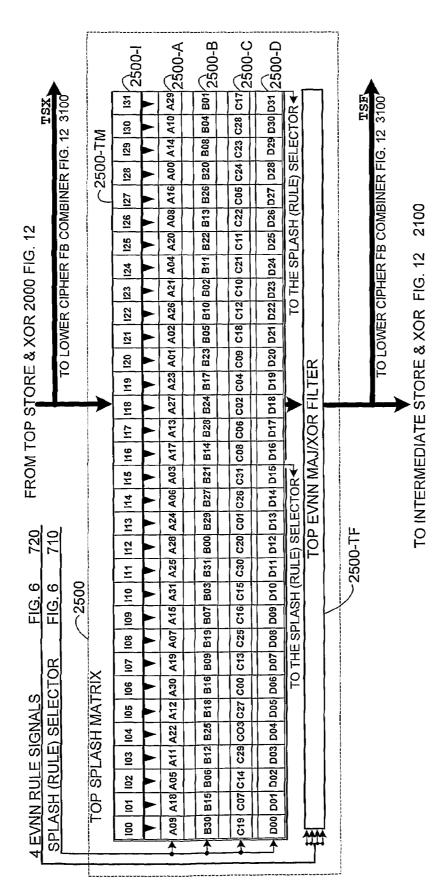

FIG. **9** is a simplified block diagram which illustrates the displacement architecture of the Top and Bottom Splash Matrices and the relations to the Random Controller architecture of the Data Churn.

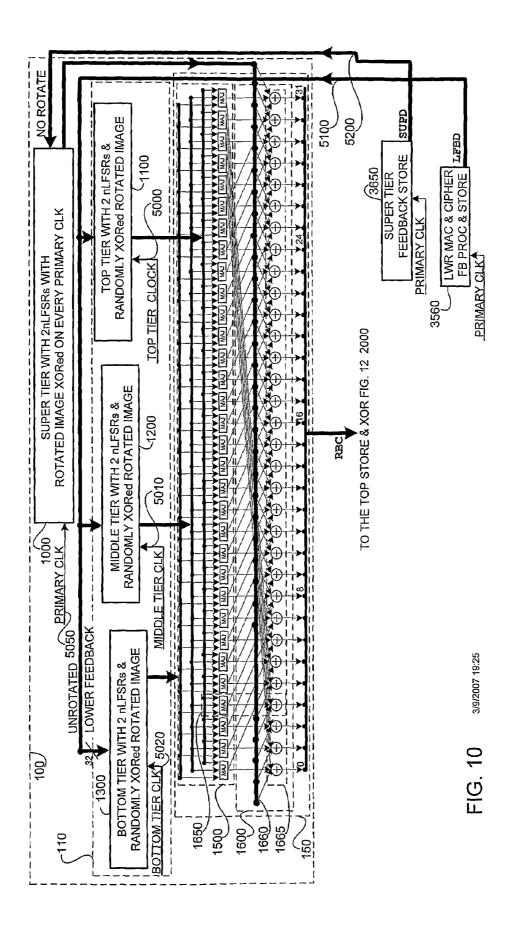

FIG. 10 is a is a simplified block and circuit diagram illustrating the interaction of the outputs of the 4 tiers of the Register Bank combined by the hybrid filter four tier combiner

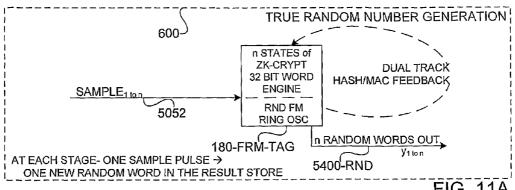

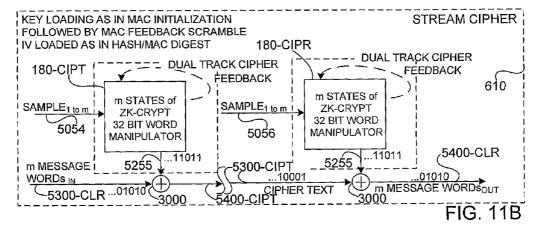

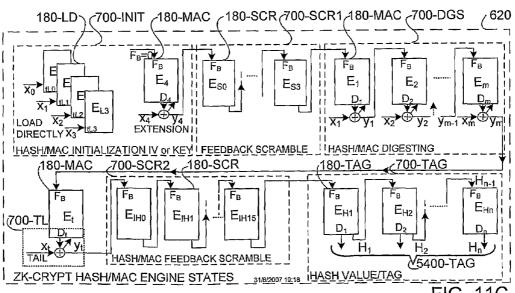

FIG. 11A is a simplified block diagram illustration of a preferred embodiment configured and initialized as a True Random Number Generator. FIG. 11B is a block diagram of a pair of preferred embodiment Engines configured as stream ciphers. FIG. 11C depicts the Engine states operative to initialize, digest and output Hash/MAC Hash-Value/MAC Tags.

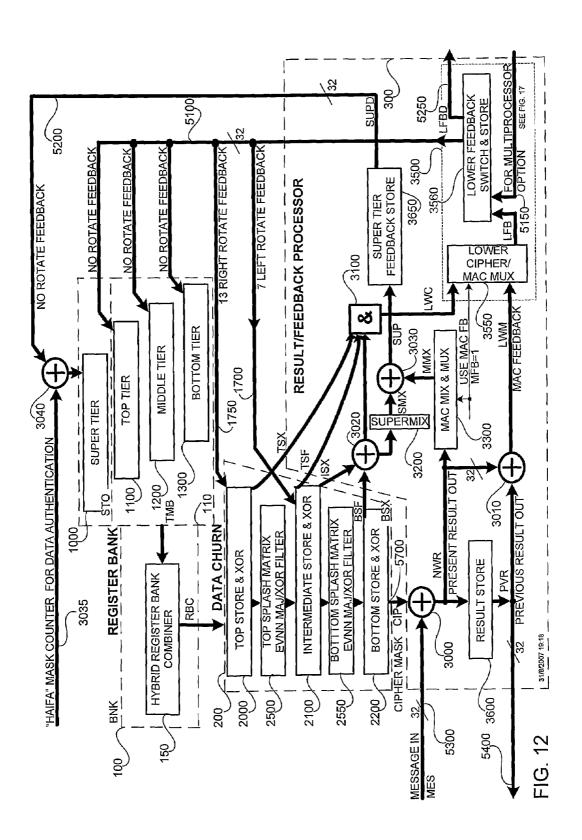

FIG. 12 is a simplified block diagram of the Register Bank, the Data Churn and the Result/Feedback Processor, wherein the word variable labels are shown to aid in understanding the description of orthogonality and of obviated Message modification.

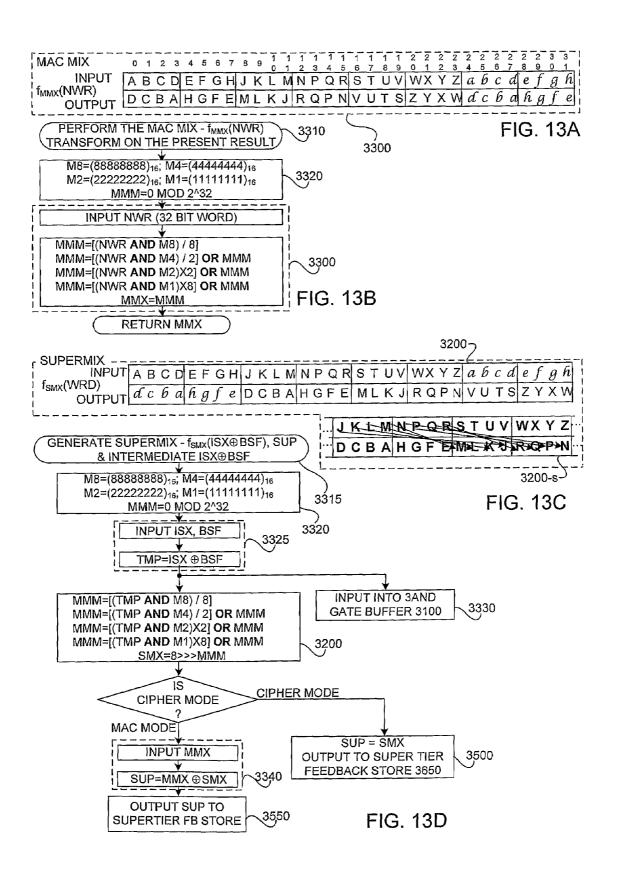

FIGS. 13A-13D are simplified block diagram illustrations of the hardware and software implementations of the two displacement filters which comprise the transforming elements of the Super Tier feedbacks.

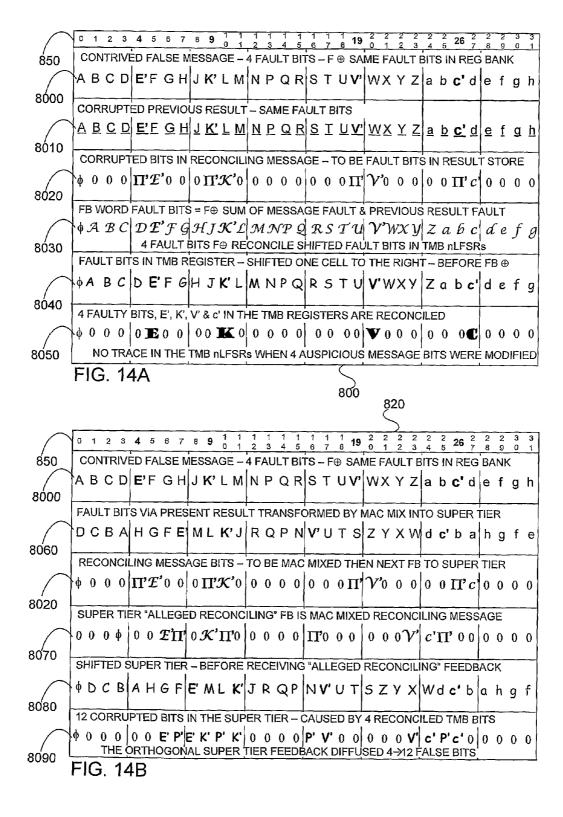

FIG. 14A is a simplified block diagram illustration of an example which typifies a message modification attack wherein four bits are complemented (a modified message) in one Primary Clock cycle, and in the next cycle, the modified bits in the TMB section of the Register Bank are reconciled; leaving no trace of the "criminal" modification in the Message Word stream.

FIG. 14B is a simplified block diagram illustration of how the same four bit aberrated message modification attack complements an orthogonal set of bits in the Super Tiers. In the next Primary Clock cycle, the modified bits in the TMB Tiers are reconciled; whereas 12 falsely complemented bits leave an impossible to reconcile trace of the "criminal" modification in the Super Tier.

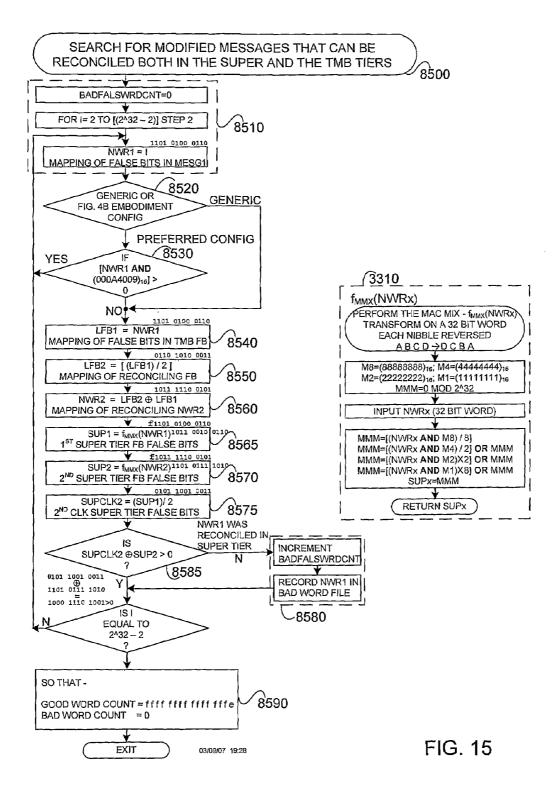

FIG. **15** is an explicit flow chart of the method which describes the orthogonality of the MAC MIX Feedback and the Lower Feedback for all possible Message Word modifications, typically for all generic subsets of nLFSR configurations in the Register Bank; i.e., all 2<sup>31</sup> possible false Message Words.

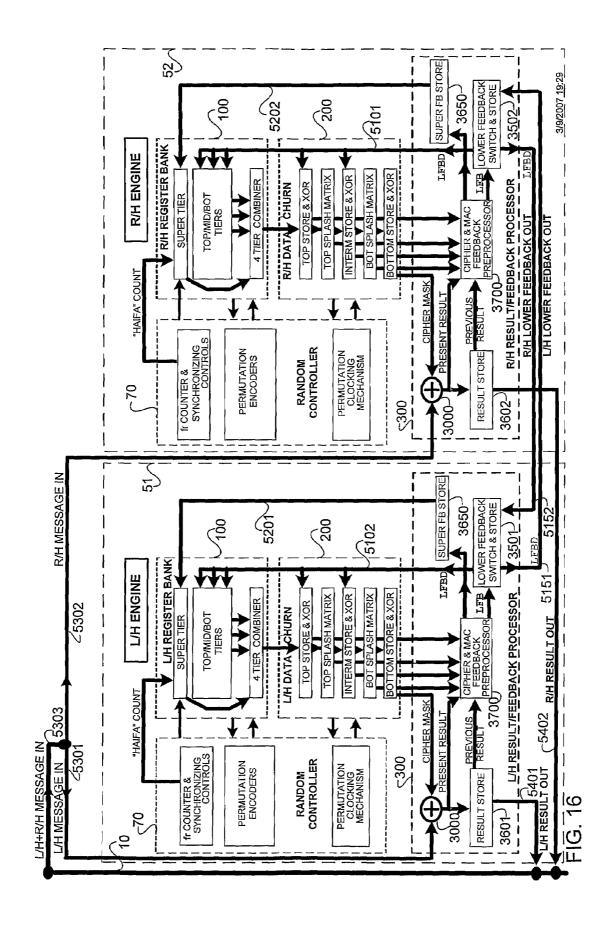

FIG. 16 is a simplified block diagram illustration of a concatenation of two preferred embodiment Engines operative to optionally "swap" the pair's Lower Feedback, e.g., the R/H (Right Hand) Lower Feedback is switched into the L/H Lower Feedback Store, and the L/H Lower Feedback is switched into the R/H Lower Feedback Store. As the units are identical, in one configuration the Engines operate separately, without shared feedback, wherein one Engine deciphers while the second Engine typically is operative to authenticate the same encrypted Message file.

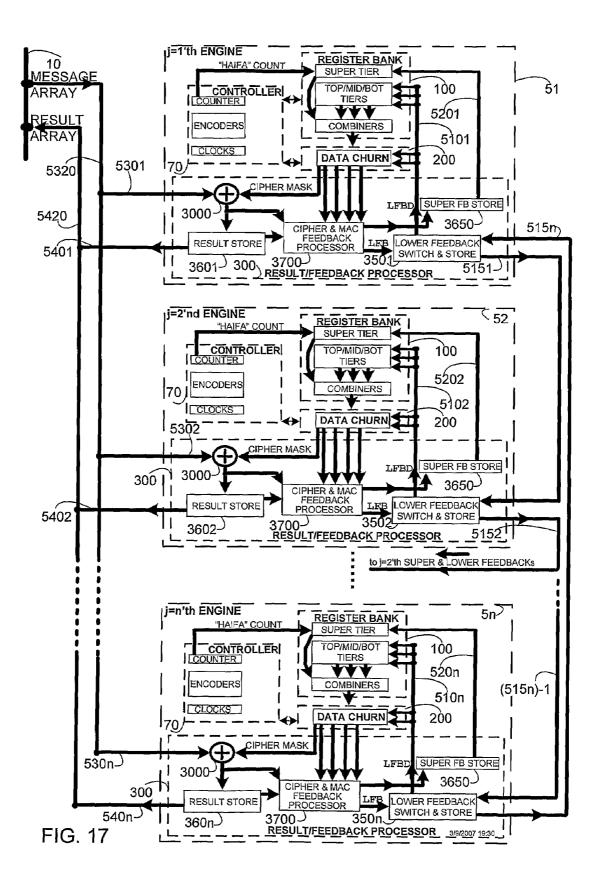

FIG. 17 is a simplified block diagram illustration of a concatenated structure of n typically identical Engines,

wherein the Lower Feedback generated in the j'th Engine is switched into the Lower Feedback Store of the (j+1 mod n)'th Engine. The concatenated Engine's throughput typically is increased n times at the same clock speed, and is more cryptocomplex than n concatenated Engines without shared feedback. Each Engine's Super Tier feedback is self-recirculated as in the single Engine preferred embodiment.

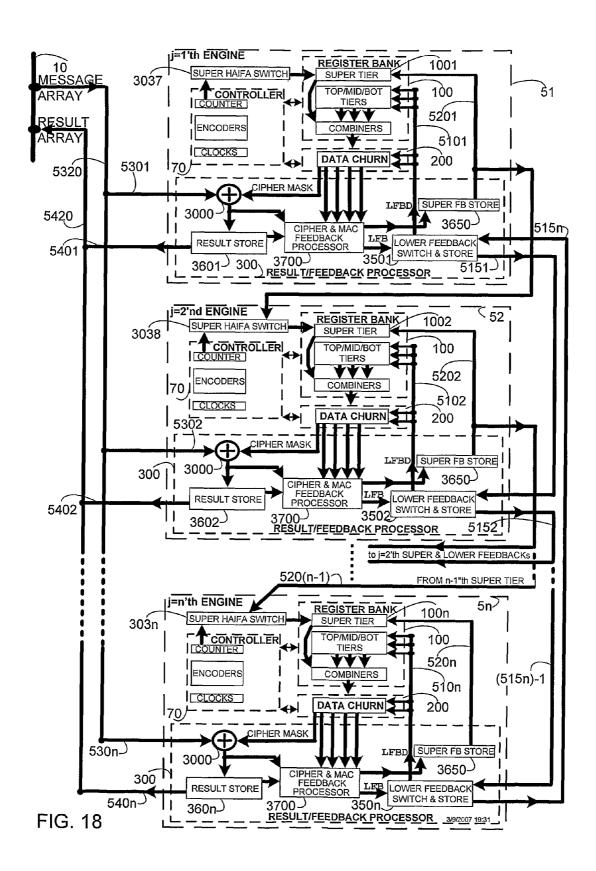

FIG. 18 is a simplified block diagram illustration of a concatenated structure of n typically identical Engines, wherein the Lower Feedback generated in each j'th Engine is switched into the Lower Feedback Store of the (j+1 mod n)'th Engine; and each Engine's Super Tier feedback is self-recirculated as in the single Engine preferred embodiment; and simultaneously the orthogonal Super Tier feedback of each of the first of the (n-1)'th concatenated Engine's Super Tier is also XOR combined into its next near neighbor's Super Tier. The concatenated Engines throughput typically is increased n times faster at the same clock speed, and is more robust than n concatenated Engines without shared feedback.

# DETAILED DESCRIPTION OF CERTAIN EMBODIMENTS

In all of the adversarial attacks described herein, it is assumed that the attacker has auspiciously chosen the time 25 and the corrupting bits, so that the Random Controller 70 shown explicitly in FIG. 6, is not adversely affected by binary state variables in either the Register Bank 100 or the Data Churn 200. This is a reasonable assumption, as any changes of Random Controller variables typically irreconcilably corrupt the permutations in the 32 Bit Word Manipulator, thereby eliminating any chance of success.

In the illustrated embodiment, data lines connecting modules of the 32 Bit Word Manipulators and the Result/Feedback Store are typically single word, typically 32 bit transmission lines or word sized busses.

Note that

- All false or probably false variable words are designated in Bold, e.g., CIP<sub>j+3</sub>. Provably false variables are underlined herein, e.g., MES<sub>j+1</sub>.

- 2) Often it cannot be demonstrated that a single word variable is false (or true), but the expression can be shown to be false, where an expression shown to be false is indicated by underscoring, e.g., CIP, \(\phi\)MES,.

FIG. 1A is a simplified block diagram of a Deterministic 45 Random Number Generator configured as a Data Authentication System 120 operative to accept a string of Message Words which uniquely aberrate the state variables of Data Authentication System 120 such that subsequent to the aberration of the plurality of state variables of Data Authentication 50 System 120; Data Authentication System 120 is in a uniquely defined state, operative to generate a unique deterministic random number string, which typically cannot be generated by another reasonably computable Message Word string; and especially in instances typified by a simply modified Message string; e.g., "... sum of \$5.00..." changed to "... sum of \$500.00..." in a meaningful valid Message string.

Typically, valid sequences of Message Words MESs are input to the Data Authentication System 120. At clock cycle k, a valid Message Word  $\mathrm{MES}_k$  is input into (word wise) XOR gate 3000 to be summed to a pseudo-random word  $\mathrm{CIP}_k$ , the output of the 1-Way Randomizing function 210 thereby outputting a Present Result  $\mathrm{NWR}_k$ . Present Result  $\mathrm{NWR}_k$  is to be stored in the next clock cycle in the Result Store 3600;  $\mathrm{NWR}_k$  is input as the  $\mathrm{SUP}_k$  to be functionally affected, stored and transmitted on the next clock cycle by the  $\mathrm{1}^{st}$  Orthogonal Feedback Generator & Store 3800; and is input into the

16

(wordwise) XOR gate 3010 to be summed to the Previous Result PVR<sub>k</sub>. The output of XOR gate 3010 is input as LBF<sub>k</sub> to be functionally affected, stored and transmitted in the next clock cycle by the  $2^{nd}$  Orthogonal Feedback Generator & Store 3500.

The  $1^{st}$  and  $2^{nd}$  Orthogonal Feedback Generator & Store **3800** and **3500** processes may be any linear function process, including simply storing the input at one clock cycle, and transmission of the same input word without change, once clock cycle later; e.g., the value  $SUP_x$  is identical to the value  $SUP_{x+1}$  one clock cycle later; the value  $LBF_x$  is identical to the value  $LBFD_{x+1}$  one clock cycle later. Output of the  $1^{st}$  Orthogonal Feedback Generator & Store **3800** SUPD, is input into Super Register Array **130** on the next clock cycle. Output of the  $2^{nd}$  Orthogonal Feedback Generator & Store **3500** SUPD is input into Lower Register Array **140** on the next clock cycle.

The Super and Lower Register Arrays 130 and 140 respectively are composed of memory registers wherein SUPD and LBFD are XOR summed into internal values of the Super and Lower Register Arrays 130 and 140. The Super and Lower Register Arrays 130 and 140 may be configured in a large plurality of ways, with included permutations, so long as every bit of SUPD and LBFD affect the state variable equations of the register arrays. The outputs of the Super and Lower Register Arrays 130 and 140 are RBCS and RBCL, respectively to be input into the 1-Way Randomizing Function 210.

The 1-Way Randomizing Function **210** comprises, typically, of logic and memory wherein each bit of the RBCS and RBCL words diffuse into the binary equations of the output the Cipher Mask CIP.

A false bit in the Message In Word MESS is only reflected in the x+2'th clock Cipher Mask CIP. Therefore, a sequence of two Message Words  $\text{MES}_j$  and  $\text{MES}_{j+1}$  can first corrupt (change a true bit or bits to a false bit or bits) and then reconcile (flip the corrupted bit(s) back to the valid state), without being affected by  $\text{CIP}_j$  or  $\text{CIP}_{j+1}$ .

To prove the efficacy of the dual feedback system, fault vectors are generated typically wherein defined "1" bits in the vector are false and bits defined as "0" are true. The XOR symbol is used to demonstrate corruption and reconciliation of binary variables. False means opposite polarity (complemented) True; therefore if a true binary value, T, is equated to "0", and F a false value to "1" then conventional XOR logic holds as:

# $T \oplus T = T$ ; $T \oplus F = F$ ; $F \oplus T = F$ ; and $F \oplus F = T$ .

If a Message bit is false and is encoded (XORed to assure a change in the feedback) with a true bit of a Cipher Mask CIP,, the result is the opposite polarity of the truth, hence false. If the next Message Word causes a new false feedback bit or bits to be XORed to the corrupted (false) bit(s), and to all of them and to them only, the resulting bit or bits are reconciled, leaving no apparent trace.

The input equation to the 1<sup>st</sup> Orthogonal Feedback Gen-60 erator & Store **3800** at time t is:

SUP<sub>t</sub>=CIP<sub>t</sub>⊕MES<sub>t</sub>—which is quite simple. In such attacks SUP is known, and except for small corrupt/ reconcile sequences, is the valid original feedback. The attacker can change MES at will.

The input equation to the  $2^{nd}$  Orthogonal Feedback Generator & Store **3500** at time t is:

2) LBF<sub>t</sub>=CIP<sub>t</sub> $\oplus$ MES<sub>t</sub> $\oplus$ CIP<sub>t-1</sub> $\oplus$ MES<sub>t-1</sub>.

conversely, the in those instances where a Message Word at time j+1 causes a faulty output to generate a fault in both the Super and Lower Register Arrays rearranging equations 1) and 2):

3) MES<sub>j+1</sub>=CIP<sub>j+1</sub>⊕SUP<sub>j+1</sub>—bitwise XOR causes same 5 bits to be flipped in the false Message and in the falsified Feedback.

and the false vector for  $LBF_{j+1}$  will be the same as for  $\underline{SUP_{j+1}}$  as the previous Message Word and the previous Cipher Mask were true:

4)  $MES_{j+1} = CIP_{j+1} \oplus LFB_{j+1} \oplus CIP_j \oplus MES_j$ .

Assume that Adversary desires to reconcile the Super Register Array 130. He must use the same Message Word and generate identical SUP<sub>j+2</sub> feedback to reconcile the Super Register Array 130. Therefore:

5) The false vector of  $\overline{\text{MES}}_{j+2}$ =the false vector of  $\overline{\text{MES}}_{j+1}$  and therefore the false vector of  $\overline{\text{SUP}}_{j+2}$ =the false vector of  $\overline{\text{SUP}}_{j+1}$  to reconcile the falsified bits in the Super Register Array 130.

However, if the false vector of  $\underline{MES_{j+2}}$ =the false vector of  $\underline{MES_{j+1}}$ ;

the  $2^{nd}$  Orthogonal Feedback Generator & Store **3500** will generate from equation 2):

6) LBF<sub>j+2</sub>=CIP<sub>j+2</sub>⊕MES<sub>j+2</sub>⊕CIP<sub>t-1</sub>⊕MES<sub>j+1</sub> wherein the LBF<sub>j+2</sub> two clock later will be the original "true" valid feedback vector which does not reconcile the corrupted binary state variables in the Lower Register Array 140.

if the Adversary attempts to generate a rectifying vector for the Lower Register Array **140**, he would send the original Message MES<sub>j+2</sub> at clock j+2, therefore from equation 2):

7) LBF<sub>j+2</sub>=CIP<sub>j+2</sub>⊕MES<sub>j+2</sub>⊕CIP<sub>j+1</sub>⊕MES<sub>j+1</sub>, repeating the previous false vector, which resides in the Result 35 Store 3600

consequently from equation 1), at the j+1'th clock wherein the Message Word and the Cipher Mask are both original values, the Super Register Array will not be reconciled as:

8) SUP<sub>j+2</sub>=CIP<sub>j+2</sub>⊕MES<sub>j+2</sub>. The variables are all true 40 original variables, and the feedback to the Super Register Array 130 is the original uncorrupted feedback, which cannot reconcile the corrupted bits in the Super Register Array 140.

In the flow chart of FIG. 15 function  $f_{MMX}(NWR_x)$  3310 45 can be replaced by any linear transformation, including outputting the previously clocked input word, without affecting the protection to be shown herein. A beneficial condition for a Data Authentication System is that a change of a bit in a Message word immediately diffuses into the inputs of the 50 binary equations of a plurality of state variables in the Super and Lower Register Arrays 130 and 140 and into the 1-Way Randomizing Function 210.

As seen, FIG. 1A is a simplified functional block diagram illustration of a data hashing system constructed and operative in accordance with an embodiment of the present invention. As shown, the data hashing system operative to hash an incoming string of message words, thereby to generate a hash value tag comprising a deterministic random number string which uniquely identifies the incoming string of message 60 words

The system typically includes first and second register arrays, at least one 1-way at least pseudo-randomizing functionality; and a set of at least first and second orthogonal feedback word stream generators operative to generate a set of at least first and second orthogonal feedback streams of message words respectively. The feedback word stream generators of the system of the

18

erators typically apply respective permutations to the incoming string of message words as described in detail herein. The first and second feedback streams are combined into the first and second register arrays respectively. The at least pseudorandomizing functionality typically accepts input from the register arrays and generates at least pseudo-random output which, in combination with a present word in the incoming string, is provided to the stream generators.

The orthogonal feedback streams are typically characterized by orthogonality, in that every possible modified incoming string of message words which differs by at least a single word from an original incoming string of message words has at least one of the following two characteristics (a) and (b):

a. the modified incoming string causes a corrupting first feedback stream generated by applying a permutation to the modified incoming string, when combined into the first register array, to corrupt the first register array, relative to the same first register array into which a non-corrupting first feedback stream, generated by applying the permutation to the original incoming string, has been combined; and/or

b. the modified incoming string includes at least one reconciling word which enables the modified incoming string, when permuted to form one first feedback stream which is combined into the first register array, to reconcile the first register array relative to the same first register array into which a modified first feedback stream, formed by permuting the original incoming string of message words, has been combined, however the at least one reconciling word in the modified incoming string of message words causes a corrupting second feedback stream generated by applying a permutation to the modified incoming string, when combined into the second register array, to corrupt the second register array, relative to the same second register array into which a non-corrupting second feedback stream, generated by applying the permutation to the original incoming string, has been combined.

Typically, the first feedback stream is a function of a present word in the incoming stream and the second feedback stream is a function (typically a different function) both of the present word and of a previous word, in the incoming stream.

FIG. 1B is a simplified block diagram of a Tag validation system operative to certify the Tag output of the Data Authentication System 120 of FIG. 1A. The apparatus consists of the Data Authenticating System 120 of FIG. 1A, and a Tag validating system comprising:

- a) a switch **125** which is closed to output the Hash-Value Tag subsequent to the Hash Digesting sequence;

- b) a Hash-Value Tag validator 195 to compare computed Tags against stored Tags;

- c) a Hash-Value Tag Store 190, operative to simultaneously output true Hash-Value Tags relevant to the application file that the Data Authentication System 120 has digested.

Same Index Tag words from the Data Authentication System 120 and the Hash-Value Store 190 are simultaneously input into the bitwise XOR gate 3020. Example word sequences 1800 from the Data Authentication System 120 and 1810 from the Hash-Value Store are bitwise summed in XOR gate 3020 operative to output an example result sequence 1820. Any detected false bits, e.g., mistaken  $D_{16}$  (1101 $_2$ ) in sequence 1800 appeared instead of  $9_{16}$  (1001 $_2$ ) such that the detecting word 0004 0000 $_{16}$  is more than zero, and the "More than Zero" Comparator 3015 outputs a bit sequence 0100, denoting that the second word of data sequence 1820 is faulty.

Typical but not limiting uses of the efficient fast, low energy hashing functions of certain preferred embodiments,

typically in conjunction with the stream cipher and true random number generation functions of certain preferred embodiments of this patent include:

- a) a Hash-Value Boot Tag 1900, to ascertain virus-free, typically perfect booting of a computing device;

- b) an automobile manufacturers keyed Tag 1905, assuring that rogue mechanics cannot enable damaging changes of automobile engine parameters;

- c) a Tag 1910 to enable secured downloading of television (TV) Messages;

- d) a Tag 1915 to certify initialization of business groups' (Corporation) mobile telephones; and,

- e) a Tag 1990 to protect rogue initialization of a communication link to a Corporation Hotline.

Vulnerable Word Manipulators are now described.

FIGS. 2A and 2B depict two simplified data authentication architectures, which are a subset of functions in certain preferred embodiment, with a single Message Word modifying feedback. The purpose of these two demonstration Engines is to intuitively present the dangers of single track feedback data 20 authentication systems with massive diffusion, where the adversary can control feedback to the pseudo-random number generating Word Manipulators. It is assumed that the astute adversary who knows the architecture has chosen auspiciously, which Message Words can aberrate the Engine 25 without affecting external parameters. A poor choice typically obviates any chance of success.

The 32 bit Word Manipulators 91 of Engines 1 and 2 of FIGS. 2A and 2B are identical.

FIG. 2A is a "Hash Attacker's Delight", as the adversary 30 knows the method and apparatus of the simple Engine, and typically generates a meaningful pre-image attack by contriving four consecutive Message Words MESs (input via transmission lines 5300). In the Result and Feedback Processor 302 of FIG. 2B one memory buffer was added (not identical 35 to Result and Feedback Processor 301 FIG. 2A), the Result Store 3600. Result Store 3600 in FIG. 2B cannot be in a valid state after a first falsified Message Word has been introduced; Store content is false, the Hash-Value/MAC Tag is false and the attack fails.

In both Engines 1 and 2, the attack starts with a true state space following valid initialization and a series of j valid 32 bit Message Words MESS, input via parallel transmission 45 lines 5300. For simplicity it is assumed 1≤j. The true Message Words MESs have been XORed to a true Cipher Mask, the output of Bottom Store & XOR 2005 BSX, to produce a feedback word to be stored in 3601 in FIG. 2A and Feedback Store 3501 in FIG. 2B. The output feedback word output 50 (delayed) on the next cycle, LFBDs on transmission lines 5101 and 5199 in FIGS. 2A and 2B, is true, and is XOR summed into the valid state Register Bank 102 on the next clocked cycle. As Register Bank 102 is in a valid state, the deterministic Logic Combiner 151 of the Register Bank with 55 Combiner 101, outputs a valid word RBC into the Data Churn **201**. The Logic Combiners **151** have no memory, and the output RBC is only a function of its inputs. Therefore if an input is true, the output is also true; similarly, if the input is false, the output is typically but not provably false.

Simultaneously, feedbacks on transmission lines 5101 and 5199 (FIGS. 2A and 2B) are input into the Top and Bottom Store & XORs in 2000 and 2005, via Filters A and B, 2001 and 2002. Filters 2001 and 2002 in certain preferred embodiments are deterministic rotations of the input words. As the Filters are deterministic, if feedback words on transmission lines 5101 or 5199 are valid, Filters A or B outputs are valid

20

respectively. If Filter A and B inputs are false, their outputs typically corrupt the binary state variables in the Data Churn

Store & XOR buffers in all embodiments output XORed previously clocked input with a presently clocked input. A typical Store & XOR cell, 2205 is shown in FIG. 3B. In FIG. 3B the storage cell 6025 "waits to accept" the NXOR summed in 6015 input bit  $X_{(i,\ell)}$  output from XOR 6013 of the Hybrid Filter of FIG. 3A, with a complemented feedback bit  $F'_{(k,t)}$  at the next clock, where k=i+7 mod 32; and during the present clock interval XOR 6010 generates the Store & XOR cell output  $Y_{(i,t)}$  comprising XOR sums of  $X_{(i,t-1)} \oplus F_{(k,t-1)}$  and  $X_{(i,t)}$ . Note that in certain preferred embodiments of FIGS. 6, 10 and 12, the LFBD feedback is not fed to the Bottom Store & XOR as shown in FIG. 3 to reduce correlation between the Cipher Mask word CIP and LFBD.

Assume at clock cycle j+1, a first false Message Word  $MES_{i+1}$  in FIGS. 1 and 2 causes an immediate false LFB<sub>i+1</sub> word "waiting" to be input into Result\Feedback Store 3601 in FIG. 1 and into Feedback Store 3501 in FIG. 2. One clock later output LFBD<sub>i+2</sub> on lines **5101** and **5199** is "waiting" to corrupt the Register Banks 102 and the Data Churns 201 in FIGS. 1 and 2, at the start of the j+3'th clock cycle. During the j+1 and j+2 cycles,  $CIP_{j+1}$  and  $CIP_{j+2}$  Cipher Masks were true, as the 32 Bit Word Manipulators 91 in FIGS. 1 and 2 were in a valid state. At the j+3 clock  $CIP_{j+3}$  is almost surely false, as the Register Banks 102 and the Data Churn 201 have been corrupted by feedback.

On the j+3'th clock we are sure that the active shift registers in the Register Banks 102 and that the Top 2000 and Bottom 2005 Store & XORs stores' outputs contents are false, as they are corrupted by the feedback word generated two cycles earlier, LFB $_{j+1}$ . If the inputs into the Logic Combiners 151 and or the Logic Data Churns 202 are all true, the respective outputs are true. However, false inputs do not necessarily produce false outputs. The Data Churns 201 are corrupted by the feedback word  $LFB_{j+2}$  as it was "aimed at the moving targets" in the Register Banks 102.

if subsequent Message Words are either reconciling words, or original valid words. If the last Hash/MAC Digest Result 40 Store & XOR cell 2200-i (caused by an  $F_{(k, t-1)}$  false feedback bit into the Register Bank 101 or the shifted 7 left feedback bit) is operative to affect the result of the Storage Cell 6025 in the t+1 clock cycle; and a false input  $X_{(i,t)}$  is operative to affect a false  $Y_{(i,t)}$ . If both the Storage Cell output and the Hybrid Filter **2100**-*i* output are false, the cell output into the Cipher Mask output is true. If one or the other only is false the output is false. In very rare cases, are all the bits in the Y, outputs of the stores in FIGS. 1 and 2 true if one or more LFB bits were false. However, if all of the scrambled input bits into the filter cell 1650 emanating from the RBC output and all the feedback F' bits are true for four consecutive clock cycles, the Top and Bottom Store & XORs in 2000 and 2005, respectively can harbor no trace of previous false inputs. Note that complex permutations without memory are not real impediments for this Message modification attack.

We know that the Register Banks 102 are corrupted by a first false word. We are not sure if the outputs in FIGS. 1 and **2**, RBC<sub>i+3</sub> are corrupted, neither do we know if an individual bit was or was not falsified in the Store & XORs. As in preferred embodiments, a single false feedback variable diffuses to 8 or 9 binary variable equations of an RBC word and to most of the binary equations of the Cipher Mask CIP. We know that the contents of at least two tiers in the bank of feedback shift registers of 102 have been corrupted by the first false feedback word, and we are reasonably sure that the contents of both the Top and Bottom Register Stores in 2000 and 2005 are corrupted. We know that the Cipher Mask CIP is

almost certainly but not provably false. (Only a rare combination of at least 2 corrupt values typically leads to a true Cipher Mask CIP output from Bottom Store & XOR 2005.)

A determined attacker has the resources to make an intelligent guess (in a MAC application) or find a way (see FIG. 5) to contrive a j+2 second false Message Word MES (in a Hash Application) that can reconcile all corrupted bits in the Register Bank 102 state variables. If false state variables of the Register Bank have been reconciled, then all state (stored memory) variables of the Register Bank are true, and the outputs of the Register Banks 101, RBC, feeding the Data Churn are true.